FPGA/SoC教学实验箱

型号:XQ7Z15-TEB

1、产品概述

? FPGA/SoC教学实验箱,由箱体、FPGA底板、FPGA核心板、实验拓展板、LCD触摸屏、FPGA下载器及相关实验配件组成;

? 基于Xilinx Zynq-7000 SoC高性能低功耗处理器,集成PL端Artix-7架构可编程逻辑单元数量为74K及PS端双核ARM Cortex-A9,主频766MHz;

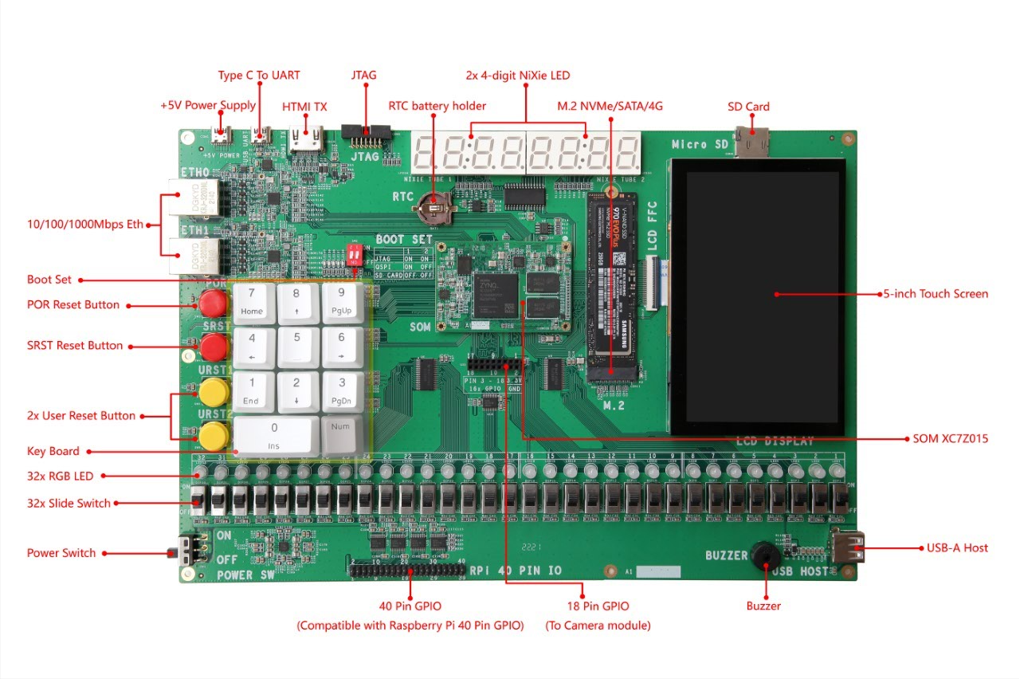

? FPGA底板资源有:2位BOOTSET、POR(PS POR复位)、SRST(PS软复位)、URST1(用户复位2)、URST2(用户复位2)、Key Board、Micro SD、2x千兆网络、HDMI OUT、RTC座、JTAG、8位LED数码管、M.2(SATA/4G)、USBUART、USB HOST、5寸LCD、蜂鸣器、32位拨动开关、32位RGB LED灯、16PIN GPIO、40PIN树莓派标准IO接口;

? 拓展板支持直流电机、步进电机、面包板、标准40PIN树莓派IO(兼容树莓派模块),实验平台丰富灵活。

? 根据实际课程教学要求提供Verilog、VHDL语言的实验例程。

? 实验指导手册包括实验目的、原理、步骤及源码解析等;适用于计信、通信、测控、电子等教学。

? 核心板采用精密工业级B2B连接器,可用于科学研究、毕业设计、电子竞赛、产品开发使用;

2、产品组成

FPGA/SoC教学实验箱可根据实际课程需求提供Verilog、VHDL实验例程,实验指导手册包括实验目的、原理、步骤及源码解析等,注重实验的过程,内容详实且丰富,IO接口(兼容树莓派模块)。

FPGA实验箱正面图

3、硬件参数

FPGA主板资源框图

表1FPGA实验主板硬件参数

CPU | Xilinx Zynq SoC XC7Z015-2CLG485I:Artix-7+双核ARM Cortex-A9,ARM主频可高达766MHz,支持6.25G的高速SerDes;Logic Cell-74K、DSP Slice-160。 |

ROM | PS 端:512MByte SD NAND FLASH |

PS 端:256Mbit QSPI NOR FLASH | |

RAM | PS 端:单通道 32bit DDR 总线,1GByte DDR3 |

OSC | PS端:33.33MHz |

PL端:25MHz | |

B2B Connector | 2x 100pin 公座 B2B 连接器,2x 100pin 母座 B2B 连接器,共 400pin,间距 0.4mm,合高 4.0mm |

LED | 2x供电指示灯(底板1个,核心板1个) |

4xPS端用户指示灯(底板2个,核心板2个) | |

2x PL端用户指示灯(底板2个) | |

1x PL端DONE指示灯(核心板) | |

32x RGB LED | |

KEY | 2x复位按键,包含1个POR复位和1个软复位 |

SWITCH | 32x用户拨动开关 |

1x电源拨动开关 | |

键盘 | 1x小键盘11按键 |

HDMI | 1x HDMI OUT |

数码管 | 2x四位八段LED数码管 |

RTC | 1x CR1220 |

蜂鸣器 | 1x蜂鸣器 |

Ethernet | PL端:1xRGMIIRJ45接口,10/100M/1000M自适应 |

PS端:1xRGMIIRJ45接口,10/100M/1000M自适应 | |

SD | 1x Micro SD接口 |

USB | 1x USB 2.0 HOST接口 |

UART | 1x UART,USB Type-C转串口 |

JTAG | 1x 14pinJTAG接口,间距2.0mm |

BOOT SET | 1x 2bit启动方式选择拨码开关 |

LCD | 1x RGB LCD接口 |

M.2 | 1x M.2接口,可接NVMe硬盘、4/5G模块 |

GPIO | 1x树莓派40Pin标准接口(可接树莓派模块) |

POWER | 1x5V@2A直流输入,USB Type-C电源接口 |

表2实验拓展板参数

电机接口 | 2x直流电机1个、步进电机1个 |

Camera接口 | 1x 24pin CMOS FFC,pin间距0.5mm |

面包板 | 1x插孔200个 |

LED | 6xLED |

表3 FPGA下载器特性

10pin/14pin JTAG接口 | 支持 |

编程速率 | 750KHz到24MHz可选 |

VREF电平范围 | 1.5V~5.0V |

支持Xinlinx器件 | 支持FPGA、SoC、CPLD、PROM等 |

支持软件 | ISE、iMPACT、ChipScope、Vivado等软件 |

IO电压 | 自动检测和适应I/O电压,支持5V(TTL)、3.3V(LVCMOS)、2.5V、1.8V和1.5V接口电平器件 |

软件参数

表4

VIVADO版本号 | Vivado2018.3 |

4、教学资源

(1) 提供芯片数据手册、底板原理图;

(2) 提供Verilog和VHDL实验例程。

(3) 提供完整的实验代码,以及适合教学的《教学实验指导手册》,教学实验主要包括:

? FPGA实验环境搭建与Vivado开发基础

? 组合逻辑实验

? 时序逻辑实验

? FPGA基础外设实验

? 综合实验

5、机械尺寸

表5

名称 | 长 | 宽 | 高 |

实验箱箱体 | 490mm | 350mm | 170mm |

FPGA底板 | 300mm | 200mm | / |

FPGA核心板 | 60mm | 40mm | 1.6mm |

实验拓展板 | 300mm | 80mm | / |

6、产品清单

表6

名称 | 数量 |

箱体 | 1个 |

FPGA底板 | 1块 |

FPGA核心板 | 1块 |

实验拓展板 | 1块 |

FPGA下载器 | 1个 |

5寸LCD电容触摸屏 | 1个 |

电源适配器 | 1个 |

USB to TYPE C线(1.5米) | 1根 |

HDMI线(1.5米) | 1根 |

网线(六类千兆)(1.5米) | 1根 |

SD卡读卡器 | 1个 |

SD卡 | 1个 |

实验箱资料(U盘) | 1套 |

杜邦线(母对母、公对母) | 各5根 |

40-40pin软排线 | 1根 |

撬棒 | 1个 |

7、实验例程

表7

FPGA实验环境搭建与Vivado开发基础 | FPGA实验环境搭建 |

Vivado开发基础 | |

触发器设计实验 | 同步RS触发器的设计实验 |

同步T触发器的设计实验 | |

同步D触发器的设计实验 | |

同步JK触发器的设计实验 | |

组合逻辑实验 | 多数表决器实验(源码) |

多数表决器实验(IP核) | |

四位二进制加法器实验 | |

一位8421 BCD码加法器实验 | |

时序逻辑实验 | 时钟同步状态机的设计实验 |

同步计数器74x163的实现实验 | |

移位寄存器的实现和应用实验 | |

FPGA外设实验 | LED流水灯实验 |

数码管显示实验 | |

LCD触摸屏显示实验 | |

HDMI显示实验 | |

UART回环实验 | |

键盘实验 | |

存储器读写实验 | |

RTC时钟实验 | |

蜂鸣器发声实验 | |

网络通讯实验 | |

USB通讯实验 | |

综合实验 | 电子秒表综合设计实验 |

应用XADC实现多路电压采集及显示实验 | |

DAC呼吸灯实验 | |

简易多通道示波器实验 | |

脉冲发生器实验 | |

十字交通灯实验 |

8、适用专业

微电子

通信工程

电子自动化

电子信息工程

测控技术与仪器

集成电路设计与集成系统

9、支撑课程

EDA技术

EDA技术与FPGA应用设计

数字电路与FPGA设计

Verilog HDL与FPGA数字系统设计

FPGA技术及应用

FPGA原理及应用

FPGA设计基础

FPGA设计与验证

FPGA系统与验证

基于FPGA集成电路设计

SoC FPGA 嵌入式设计和开发

CPLD/FPGA设计与应用

CPLD/FPGA与ASIC设计

硬件描述语言与FPGA设计技术

10、技术服务

协助底板设计和测试,减少硬件设计失误;

协助解决按照用户手册操作出现的异常问题;

协助产品故障判定;

协助正确编译与运行所提供的源代码;

协助进行产品二次开发;

11 增值服务

板定制设计

核心板定制设计

嵌入式软件开发

项目合作开发

技术培训